小编:本文的摘要报价地址:本文介绍了在FPGA中实现的增强的正交频部多路复用器设计,该设计使用了相反的FFT模式

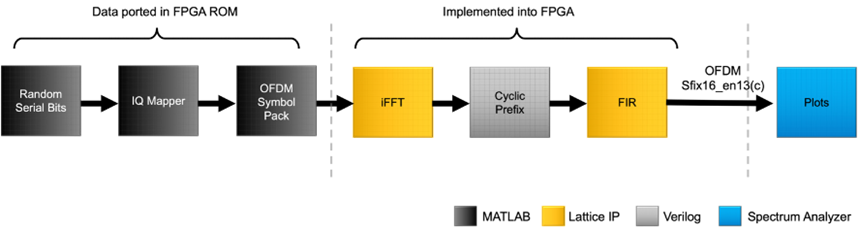

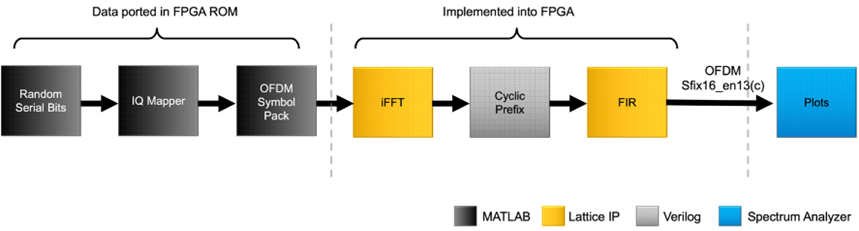

摘要本文提到的地址:本文介绍了在FPGA中实现的增强的正交频部多路复用器调制器设计,该设计在相反的FFT模式下使用晶格快速傅立叶变换(FFT)编译器IP核心,而Lattice有限脉冲脉冲回复(FIR)滤镜核心IP。该设计将解决在没有基本控制器的情况下开发复杂测试模式的通常问题,这极大地提高了无线链路测试的效率。通过直接测试模拟的前端JESD204B链接,OFDM调制器将摆脱主机控制器的期望,简化初始调试过程。该设计可以直接在晶格FPGA核心上实现,从而节省了开发周期的成本和旋转。 lattice Jesd204B IP接口链接,使用了ADI的ADI ADI的TheAdrv9029,5G RF前端评估委员会的TheAdrv9029,5G RF前端评估委员会,使用了Avant-X70 Versa评估板。简而言之,本文介绍了一个新的OFDM调制器设计结合了晶格FIR和IFFT IP内核,简化了无线链接的验证,降低了成本和经常出现的发育时间。 1。简介正交频部多路复用(OFDM)是许多无线和有线通信系统的主要技术,尤其是5G和Wi-Fi 4/5/5/5/6/7标准。 OFDM以频谱的高效率,通道褪色的稳定性和灵活性而闻名。本文描述了这些系统中遇到的常见问题的增强解决方案:需要在没有主要控制器的情况下难以生产的复杂测试模式。本文介绍了OFDM调制器的设计和实现。此功能对于无线链接测试特别有用。 设计是通过集成晶格FPGA优化快速傅立叶变换(FFT)编译器IP核心(相反的FFT模式)和有限脉冲回复(FIR)滤波器IP核心来开发的。该解决方案替换了以前的MET使用HDL编码器生成FIR过滤器和相对的FFT模块的HOD,但后者是一个有效且可靠的解决方案。晶格FFT编译器IP核心提供了前进和反向FFT模式,该模式可以配置FFT点和实现模式的数量,以确保信号处理的灵活性和效率。在此设计中,使用反向模式FFT编译器IP核心。使用Alattice Parato中的高性能数字信号处理(DSP)实现了晶格FIR滤波器IP核心。这提供了配置的数据,系数和输出数据宽度,以支持广泛的应用程序。本文还讨论了在无线链接的初始开始期间遇到的一个常见问题:缺乏FPGA输入OFDM模式的主控制器。如果要使用主机提供OFDM模式,则应在FPGA和主机之间建立匹配的接口,例如PCIE,并提供在无线链接测试之前执行测试所需的主机软件开始。这个过程不仅消耗了这种问题时及时,无效且难以调试。为了进一步增强测试过程,本文使用lattice avanttm-x70 versa versa boardby jesd204b ip链接显示了ADI 5G RF前端ADRV9029评估板中的互操作性。 ADRV9029是专为5G应用设计的四通道宽带RF收发器。该设置显示了调节器生成OFDM模式并验证无线链接的能力,而无需依赖主机,从而大大提高了测试效率。使用OFDM调制器结合了晶格FIR和IFFT IP内核,我们可以更好地验证FPGA无线链接。 2。使用FIR和IFFT IP 2.1的OFDM调制器设计。调制器的调节器设计详细信息使用各种设计技术,工具和晶格IP核心,包括MATLAB®,IFFT,FIR,FIR和MANU编码的RTL。图1显示了OFDM数据路径的高水平OFDM设计路径。 OFDM调制器输送链使用FIR功能解决方案在5G通信系统中的此调制中的解决方案。图1。调制器设计图的图1中的不同颜色在图1中确定不同的实现方法:深色-bao:由Matlab黄色形成的FPGA ROM的符号:使用晶格IP核心浅灰色实现的模块:使用MANU -MANU -MANU -MANU -MANU SPECTRUM SPECTRUM分析仪实现验证2.2。 OFDM模式生成OFDM模式发电机继续重复并输出OFDM符号及其周期前缀。在MATLAB中的FPGA ROM中预先形成,处理和存储一组随机调制符号。在随后的模块中读取ROM内容,包括IFFT IP,循环前缀模块和FIR IP,形成OFDM模式,并开发智商数据以在无线电达拉斯结束时进行馈送。下表显示了设计中使用的OFDM模式的系统参数。表1。OFDM模式系统参数2.3。唯一的功能和好处 - 与设计:用户可以直接实施此设计On FPGA核心无需外部设备。成本和时间效率:此设计减少了购买或借用外部设备并开发复杂的测试系统所需的成本和时间。全面验证:开发人员可以通过FPGA中的JESD204B IP核心建立连接,并完成从功能模拟到硬件开发到开发套件的整个测试过程。 2.4。设计过程本节讨论了OFDM调制器的设计过程,从实现晶格FPGA的实现的MATLAB模型。 2.4.1。开发过程基于晶格FPGA调制器设计过程,该过程始于MATLAB中初始模型的实现。在此阶段,需要根据所需的参数完成调制器建模。并通过功率谱密度(PSD)图验证调制器的输出。然后,SINC过滤器的调制和系数的生成符号是转移到Avant™FPGA平台。选择前卫FPGA的关键是硬核DSP模块和嵌入式内存的理想组合,可以平衡处理强度和存储容量。这些组件与ROM IP核心和FIR IP核心集成在一起,以确保处理无缝数据。此外,还需要根据形成调制符号时使用的f点ft的数量来配置其他主要的FPGA IP(例如IFT模块)。这些IP内核将包含在字母RTL字母(包括循环前缀模块)中,以生成完整的设计。为了确保正确的设计功能,需要在QuestAsim™晶格版中进行RTL级别仿真,并将仿真结果仔细地与MATLAB模拟数据进行比较,以验证其准确性。最后阶段需要在晶格FPGA开发套件中进行设计扩展。在此链接中,与RTL仿真数据相比,硬件输出的结果需要严格地进行。如果偏差在验证过程中发现,需要进行全面的演示,并在回顾阶段进行校正,以确保OFDM的调节器设计实现了一个稳定且可靠的目标(请参见图2)。 LARCLOUD 2。调制器和调制器进程2.4.2。 FPGA设计模块本节讨论用于实现DM调制器的FPGA中的模块。 2.4.2.1。在将Rommatlab生成的OFDM调制的符号分为真实和虚部,然后再转换为定点格式。然后将这些固定值转换为十六进制格式(HEX),并存储在FPGA ROM中。在用户模式下,将ROM内容插入IFFT IP中。图3显示了此设计中使用的晶格ROM IP调整的示例。图3。用于存储调制符号2.4.2.2的真实部分的ROM IP配置。使用OFDM作为多载波调制技术的IFT到发射器,OFDM符号的构建过程如下:FIrst映射该调制的i和q的部分的输入位,根据OFDM符号中的子载波数量(即,IFT点的数量)(即IFT点的数量)。通过映射和分类的操作,可以构建OFDM符号域的组件。为了发送这些信号,必须将它们转换为时间域以进行表示。通过快速相反的傅立叶变换(IFT)实现此转换过程。在此调制器的设计中,每个64QAM符号都将其转换为子载波频率,并使用晶状体FFT编译器IP以反向模式转换为域时间。图4显示了此设计中使用的晶格FFT编译器IP调整的示例。图4。配置相对模式FFT编译器IP2.4.3。 圆形前缀圆形前缀是提高交付效率下可靠性的关键要素。在此设计中,OFDM符号的最后64个示例在开始时重复相同的符号。这将有助于在信号传递过程中减少互联网干扰(ISI)。如果T的iffang tut进入字母 - 手形的前缀块。 2.4.4。 FIR编译器IP数据路径上的最后一个模块是过滤器。该过滤器在OFDM域符号时作用,该符号旨在抑制子带信号的带外辐射,同时维持OFDM符号的复杂正交域性质。为了实现这一目标,FIR过滤器需要满足以下标准:式带对子带陡峭的传输带设计中的子载波,以减少保护带的要求可以满足上述停止标准。为了实现目标,需要通过窗口来实现低通滤波器 - 具体来说,窗口函数有效地切割了脉冲响应,并在两端提供了平稳的过渡到零。图5显示了频域中5个相邻子载波的图的示例,其幅度在1时标准化,频率为1y间隔为1。显示的子载体是正交的。每个子载波由域频率表示为SINC的函数。图5。在带有FIR滤波器的OFDM系统中相邻和正交子载波图的示例,通过设计的FIR滤波器处理子带OFDM信号。由于滤波器通带对应于信号带宽,因此在频带边缘附近的体积的少数载体将受到显着影响。一个主要的设计点是允许滤波器长度超过OFDM的环状前缀长度。通过使用窗口技术(结合软截止)的FIR滤波器设计,内部干扰降至最低。在此设计中,MATLAB首先用于产生具有513 TAP系数的刻度功能,然后将这些参数导入FIR编译器IP核心。图6显示了此设计中使用的晶格FIR编译器IP核心的实例。图6。FIR编译器IP配置3。OFDM Modulato的实现R Design使用Avant-X70 Versa板上在前卫-X70设备上实施。 OFDM调制器已连接到JESD204B链路层和物理层,以将数据发送到RF前端ADRV9029。总共有4个JESD204B通道,每个通道最多可达到6.144GBP。 OFDM调制器和JESD204B IP运行到ADRV9029评估板上形成的153.6 MHz时钟,请参见图7。图7。互操作性测试设置设置框图:Avant Jesd204B和ADRV90293.1。二手软件和硬件。该设计中使用的软件和硬件如下:软件:Lattice Radiant™软件Tinya®-AppMatlab硬件:Lattice AppMatlab:Lattice-X70(LAV-AT-AT-X70-2LFG1156C)Lattice-X70 Versa Arda Deversa Developta Development-evant-x7029评估委员会tiysaya ultrabe tiysaa ultrabe tiysa ultraba tiysa ultrabos tiysa ultrabe expentment-3.2。设计验证Avant-X70 Versa板和ADRV9029评估板通过JESD204B连接,并通过测试硬件互操作性证明了设计。综合性E验证过程可确保设计实施的稳定性和可靠性。以下各节描述了所使用的测试方法。 3.2.1。互操作性测试Avant-X70 Versa开发委员会通过FMC上的FMC连接到ADRV9029评估板。使用SMA线将RF信号从ADRV9029连接到Spectrum Analyzer,以获取PSD图。将图形带宽与理论值进行比较,以确保正确实现。 4。4。结果和讨论4.1。前卫-X70 Versa开发板硬件测试ADRV9029评估板的RF信号输出连接到Spectrum Analyzer,以获取PSD图。使用标记测量PSD带宽。图9显示了RF信号输出之一的PSD图。图9。从PSD频谱的硬件测试结果到频谱分析仪的主要结论如下:以矩形形状= 1052MHz -947MHz = 105MHz4.2测量的带宽。 OFDM调制器PSD映射从MATLAB模拟的MATLAB模型中放置为Spectrum Analyzer获得的PSD频谱。结果表明,MATLAB模型的PSD图的形状和带宽以及硬件测试结果的匹配。图10。MATLAB模型的OFDM PSD输出图4.3。表1中描述的OFDM模式的系统参数下的结果的评估和解释,Spectrum Analyzer获得的PSD频谱带宽的预期理论计算以及通过MATLAB模拟获得的带宽值和频谱分析仪的绘制。 5。结论5.1。一般研究和结果本文提出了基于晶格FFT编译器IP核心,FIR Filt Filter IP核心和Manu -Manu -Manu -Design RTL代码的OFDM调制器实现的方法。 Adrv9029评估委员会通过JESD204B界面互连。打架的实际结果表明该设计具有很高可靠性和稳定性。此外,理论值与Spectrum Analyzer收集的PSD频谱的带宽结果一致,该结果有效地验证了设计的功能完整性。 5.2。未来的研究表明,未来的研究可能关注以下领域:DM解调剂的开发:解调器完成回环数据路径,可以在发送的符号中恢复和评估OFDM符号。本文使用的6abbreviations

摘要本文提到的地址:本文介绍了在FPGA中实现的增强的正交频部多路复用器调制器设计,该设计在相反的FFT模式下使用晶格快速傅立叶变换(FFT)编译器IP核心,而Lattice有限脉冲脉冲回复(FIR)滤镜核心IP。该设计将解决在没有基本控制器的情况下开发复杂测试模式的通常问题,这极大地提高了无线链路测试的效率。通过直接测试模拟的前端JESD204B链接,OFDM调制器将摆脱主机控制器的期望,简化初始调试过程。该设计可以直接在晶格FPGA核心上实现,从而节省了开发周期的成本和旋转。 lattice Jesd204B IP接口链接,使用了ADI的ADI ADI的TheAdrv9029,5G RF前端评估委员会的TheAdrv9029,5G RF前端评估委员会,使用了Avant-X70 Versa评估板。简而言之,本文介绍了一个新的OFDM调制器设计结合了晶格FIR和IFFT IP内核,简化了无线链接的验证,降低了成本和经常出现的发育时间。 1。简介正交频部多路复用(OFDM)是许多无线和有线通信系统的主要技术,尤其是5G和Wi-Fi 4/5/5/5/6/7标准。 OFDM以频谱的高效率,通道褪色的稳定性和灵活性而闻名。本文描述了这些系统中遇到的常见问题的增强解决方案:需要在没有主要控制器的情况下难以生产的复杂测试模式。本文介绍了OFDM调制器的设计和实现。此功能对于无线链接测试特别有用。 设计是通过集成晶格FPGA优化快速傅立叶变换(FFT)编译器IP核心(相反的FFT模式)和有限脉冲回复(FIR)滤波器IP核心来开发的。该解决方案替换了以前的MET使用HDL编码器生成FIR过滤器和相对的FFT模块的HOD,但后者是一个有效且可靠的解决方案。晶格FFT编译器IP核心提供了前进和反向FFT模式,该模式可以配置FFT点和实现模式的数量,以确保信号处理的灵活性和效率。在此设计中,使用反向模式FFT编译器IP核心。使用Alattice Parato中的高性能数字信号处理(DSP)实现了晶格FIR滤波器IP核心。这提供了配置的数据,系数和输出数据宽度,以支持广泛的应用程序。本文还讨论了在无线链接的初始开始期间遇到的一个常见问题:缺乏FPGA输入OFDM模式的主控制器。如果要使用主机提供OFDM模式,则应在FPGA和主机之间建立匹配的接口,例如PCIE,并提供在无线链接测试之前执行测试所需的主机软件开始。这个过程不仅消耗了这种问题时及时,无效且难以调试。为了进一步增强测试过程,本文使用lattice avanttm-x70 versa versa boardby jesd204b ip链接显示了ADI 5G RF前端ADRV9029评估板中的互操作性。 ADRV9029是专为5G应用设计的四通道宽带RF收发器。该设置显示了调节器生成OFDM模式并验证无线链接的能力,而无需依赖主机,从而大大提高了测试效率。使用OFDM调制器结合了晶格FIR和IFFT IP内核,我们可以更好地验证FPGA无线链接。 2。使用FIR和IFFT IP 2.1的OFDM调制器设计。调制器的调节器设计详细信息使用各种设计技术,工具和晶格IP核心,包括MATLAB®,IFFT,FIR,FIR和MANU编码的RTL。图1显示了OFDM数据路径的高水平OFDM设计路径。 OFDM调制器输送链使用FIR功能解决方案在5G通信系统中的此调制中的解决方案。图1。调制器设计图的图1中的不同颜色在图1中确定不同的实现方法:深色-bao:由Matlab黄色形成的FPGA ROM的符号:使用晶格IP核心浅灰色实现的模块:使用MANU -MANU -MANU -MANU -MANU SPECTRUM SPECTRUM分析仪实现验证2.2。 OFDM模式生成OFDM模式发电机继续重复并输出OFDM符号及其周期前缀。在MATLAB中的FPGA ROM中预先形成,处理和存储一组随机调制符号。在随后的模块中读取ROM内容,包括IFFT IP,循环前缀模块和FIR IP,形成OFDM模式,并开发智商数据以在无线电达拉斯结束时进行馈送。下表显示了设计中使用的OFDM模式的系统参数。表1。OFDM模式系统参数2.3。唯一的功能和好处 - 与设计:用户可以直接实施此设计On FPGA核心无需外部设备。成本和时间效率:此设计减少了购买或借用外部设备并开发复杂的测试系统所需的成本和时间。全面验证:开发人员可以通过FPGA中的JESD204B IP核心建立连接,并完成从功能模拟到硬件开发到开发套件的整个测试过程。 2.4。设计过程本节讨论了OFDM调制器的设计过程,从实现晶格FPGA的实现的MATLAB模型。 2.4.1。开发过程基于晶格FPGA调制器设计过程,该过程始于MATLAB中初始模型的实现。在此阶段,需要根据所需的参数完成调制器建模。并通过功率谱密度(PSD)图验证调制器的输出。然后,SINC过滤器的调制和系数的生成符号是转移到Avant™FPGA平台。选择前卫FPGA的关键是硬核DSP模块和嵌入式内存的理想组合,可以平衡处理强度和存储容量。这些组件与ROM IP核心和FIR IP核心集成在一起,以确保处理无缝数据。此外,还需要根据形成调制符号时使用的f点ft的数量来配置其他主要的FPGA IP(例如IFT模块)。这些IP内核将包含在字母RTL字母(包括循环前缀模块)中,以生成完整的设计。为了确保正确的设计功能,需要在QuestAsim™晶格版中进行RTL级别仿真,并将仿真结果仔细地与MATLAB模拟数据进行比较,以验证其准确性。最后阶段需要在晶格FPGA开发套件中进行设计扩展。在此链接中,与RTL仿真数据相比,硬件输出的结果需要严格地进行。如果偏差在验证过程中发现,需要进行全面的演示,并在回顾阶段进行校正,以确保OFDM的调节器设计实现了一个稳定且可靠的目标(请参见图2)。 LARCLOUD 2。调制器和调制器进程2.4.2。 FPGA设计模块本节讨论用于实现DM调制器的FPGA中的模块。 2.4.2.1。在将Rommatlab生成的OFDM调制的符号分为真实和虚部,然后再转换为定点格式。然后将这些固定值转换为十六进制格式(HEX),并存储在FPGA ROM中。在用户模式下,将ROM内容插入IFFT IP中。图3显示了此设计中使用的晶格ROM IP调整的示例。图3。用于存储调制符号2.4.2.2的真实部分的ROM IP配置。使用OFDM作为多载波调制技术的IFT到发射器,OFDM符号的构建过程如下:FIrst映射该调制的i和q的部分的输入位,根据OFDM符号中的子载波数量(即,IFT点的数量)(即IFT点的数量)。通过映射和分类的操作,可以构建OFDM符号域的组件。为了发送这些信号,必须将它们转换为时间域以进行表示。通过快速相反的傅立叶变换(IFT)实现此转换过程。在此调制器的设计中,每个64QAM符号都将其转换为子载波频率,并使用晶状体FFT编译器IP以反向模式转换为域时间。图4显示了此设计中使用的晶格FFT编译器IP调整的示例。图4。配置相对模式FFT编译器IP2.4.3。 圆形前缀圆形前缀是提高交付效率下可靠性的关键要素。在此设计中,OFDM符号的最后64个示例在开始时重复相同的符号。这将有助于在信号传递过程中减少互联网干扰(ISI)。如果T的iffang tut进入字母 - 手形的前缀块。 2.4.4。 FIR编译器IP数据路径上的最后一个模块是过滤器。该过滤器在OFDM域符号时作用,该符号旨在抑制子带信号的带外辐射,同时维持OFDM符号的复杂正交域性质。为了实现这一目标,FIR过滤器需要满足以下标准:式带对子带陡峭的传输带设计中的子载波,以减少保护带的要求可以满足上述停止标准。为了实现目标,需要通过窗口来实现低通滤波器 - 具体来说,窗口函数有效地切割了脉冲响应,并在两端提供了平稳的过渡到零。图5显示了频域中5个相邻子载波的图的示例,其幅度在1时标准化,频率为1y间隔为1。显示的子载体是正交的。每个子载波由域频率表示为SINC的函数。图5。在带有FIR滤波器的OFDM系统中相邻和正交子载波图的示例,通过设计的FIR滤波器处理子带OFDM信号。由于滤波器通带对应于信号带宽,因此在频带边缘附近的体积的少数载体将受到显着影响。一个主要的设计点是允许滤波器长度超过OFDM的环状前缀长度。通过使用窗口技术(结合软截止)的FIR滤波器设计,内部干扰降至最低。在此设计中,MATLAB首先用于产生具有513 TAP系数的刻度功能,然后将这些参数导入FIR编译器IP核心。图6显示了此设计中使用的晶格FIR编译器IP核心的实例。图6。FIR编译器IP配置3。OFDM Modulato的实现R Design使用Avant-X70 Versa板上在前卫-X70设备上实施。 OFDM调制器已连接到JESD204B链路层和物理层,以将数据发送到RF前端ADRV9029。总共有4个JESD204B通道,每个通道最多可达到6.144GBP。 OFDM调制器和JESD204B IP运行到ADRV9029评估板上形成的153.6 MHz时钟,请参见图7。图7。互操作性测试设置设置框图:Avant Jesd204B和ADRV90293.1。二手软件和硬件。该设计中使用的软件和硬件如下:软件:Lattice Radiant™软件Tinya®-AppMatlab硬件:Lattice AppMatlab:Lattice-X70(LAV-AT-AT-X70-2LFG1156C)Lattice-X70 Versa Arda Deversa Developta Development-evant-x7029评估委员会tiysaya ultrabe tiysaa ultrabe tiysa ultraba tiysa ultrabos tiysa ultrabe expentment-3.2。设计验证Avant-X70 Versa板和ADRV9029评估板通过JESD204B连接,并通过测试硬件互操作性证明了设计。综合性E验证过程可确保设计实施的稳定性和可靠性。以下各节描述了所使用的测试方法。 3.2.1。互操作性测试Avant-X70 Versa开发委员会通过FMC上的FMC连接到ADRV9029评估板。使用SMA线将RF信号从ADRV9029连接到Spectrum Analyzer,以获取PSD图。将图形带宽与理论值进行比较,以确保正确实现。 4。4。结果和讨论4.1。前卫-X70 Versa开发板硬件测试ADRV9029评估板的RF信号输出连接到Spectrum Analyzer,以获取PSD图。使用标记测量PSD带宽。图9显示了RF信号输出之一的PSD图。图9。从PSD频谱的硬件测试结果到频谱分析仪的主要结论如下:以矩形形状= 1052MHz -947MHz = 105MHz4.2测量的带宽。 OFDM调制器PSD映射从MATLAB模拟的MATLAB模型中放置为Spectrum Analyzer获得的PSD频谱。结果表明,MATLAB模型的PSD图的形状和带宽以及硬件测试结果的匹配。图10。MATLAB模型的OFDM PSD输出图4.3。表1中描述的OFDM模式的系统参数下的结果的评估和解释,Spectrum Analyzer获得的PSD频谱带宽的预期理论计算以及通过MATLAB模拟获得的带宽值和频谱分析仪的绘制。 5。结论5.1。一般研究和结果本文提出了基于晶格FFT编译器IP核心,FIR Filt Filter IP核心和Manu -Manu -Manu -Design RTL代码的OFDM调制器实现的方法。 Adrv9029评估委员会通过JESD204B界面互连。打架的实际结果表明该设计具有很高可靠性和稳定性。此外,理论值与Spectrum Analyzer收集的PSD频谱的带宽结果一致,该结果有效地验证了设计的功能完整性。 5.2。未来的研究表明,未来的研究可能关注以下领域:DM解调剂的开发:解调器完成回环数据路径,可以在发送的符号中恢复和评估OFDM符号。本文使用的6abbreviations

当前网址:https://www.jling-tech.com//tutorials/web/2025/0419/738.html